《用于 3D IC 和模块集成的无线接口技术(Wireless Interface Technologies for 3D IC and Module Integration)》简介

《用于 3D IC 和模块集成的无线接口技术》

本书综合十五年的研究,本书综合了无线芯片和模块接口设计的两大技术,本书涵盖了技术基础、设计考虑和权衡、实际实现考虑,以及对神经网络、可重构处理器和堆叠SRAM中的实际应用的讨论。本书解释了两种近场无线接口技术的设计原理和应用,分别用于2.5-3D IC和模块集成,并描述了系统级性能优势,使本书成为研究人员,专业工程师和研究生进行下一代无线芯片和模块接口设计研究的重要参考学习资源。

《用于 3D IC 和模块集成的无线接口技术(Wireless Interface Technologies for 3D IC and Module Integration)》研究的内容介绍

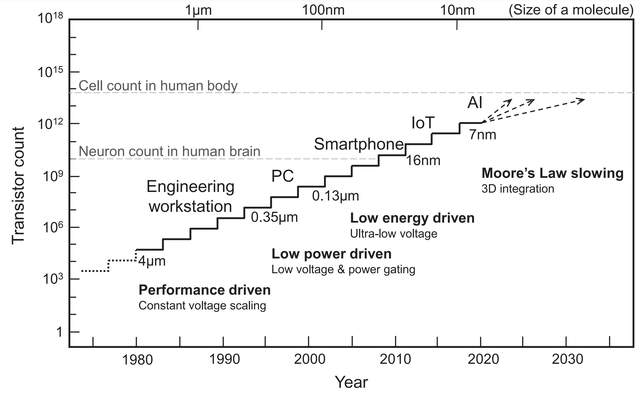

在过去的 35 年中,集成电路 (IC) 特征尺寸减小了两个数量级以上。 然而,工作电压仅降低了一个数量级。 这是因为开关晶体管栅极所需的电场不会线性缩小。 在不按比例降低工作电压的情况下进行工艺缩放,导致功率密度增加了三个数量级。 因此,功率密度已成为 IC 性能改进的限制因素。

IC进步的另一个挑战是异构芯片技术的集成。 例如,虽然逻辑功能需要高性能晶体管,但内存存储需要高密度电容器。 如果将这两种功能集成到单个芯片上,制造成本可能会高得令人望而却步。 因此,逻辑和内存是在独立的芯片上实现的,具有独立优化的工艺,而两者之间数据流经的接口已成为信息处理的瓶颈。

因此,进一步提升计算系统性能的关键在于开发芯片接口,通过优化互连来提高电源效率,消除数据传输的瓶颈。

本书的第 1 章详细阐述了 IC、芯片接口、计算机和连接器的发展以及相关挑战的讨论。其摘要指出需要将芯片互连从二维 (2D) 转移到三维 ( 3D)。 革命性接口的时机恰到好处,因为摩尔定律的放缓创造了一个机会,可以引入颠覆性技术来实现超越摩尔的性能飞跃。

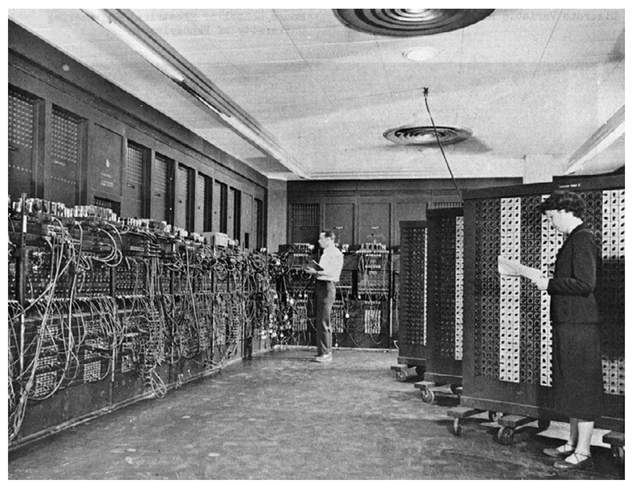

最初,发明集成电路是为了解决大型计算机系统的互连问题。 例如,第一台电子通用计算机电子数字积分器和计算机 (ENIAC) 有大约 500 万个焊点。 通过集成处理元件并将它们互连在一块硅片上,IC 消除了如此大量的手工连接。 现代 IC 将数百亿个电路元件与总长几公里的互连线连接起来。 这些连接都可以在晶圆加工过程中一举完成。 然而,随着摩尔定律的放缓,我们不能再仅仅依靠将越来越多的功能集成到单个芯片上来提高性能。 我们需要找到接口问题的革命性解决方案,以提高多芯片系统的性能。

第一台电子通用计算机电子数字积分器和计算机 (ENIAC) 有大约 500 万个焊点

我们的建议是用采用近场耦合的非接触式无线连接取代芯片之间和模块之间的机械连接,例如使用焊点和连接器的机械连接。 我们自主研发了基于磁耦合芯片互联的ThruChip Interface(TCI)和基于电磁耦合模块互联的Transmission Line Coupler(TLC)两种无线接口技术,并成功演示了1/1,000的TCI芯片接口 常规数据传输功率。

磁场可以穿透硅芯片。 它可以穿透金属互连和硅基板。 同时,它对使用电场工作的电子电路造成的干扰可以忽略不计。 由于我们基于磁耦合的接口利用了由金属线创建的线圈图案,因此它的实现可以很容易地集成到传统的晶圆工艺中。 除了保持较低的成本开销外,它还允许接口受益于持续工艺扩展所带来的性能提升。 它引入的唯一新要求是能够在三维空间缩放,或者更具体地说是将芯片减薄。

直到几年前,人们还认为很难将动态随机存取存储器 (DRAM) 芯片减薄到 30 µm 以下。 然而,据报道,最近的发展已将芯片减薄至 5 µm。 因此,在制造业对芯片薄化技术的进步寄予厚望的情况下,相关技术的开发已经开始了。

ThruChip Interface(TCI,穿透芯片接口技术)仍需克服三个挑战:(1) 功率传输,(2) 干扰 DRAM 操作,以及 (3) 散热。 我们发起了一个由日本科学技术厅支持的 ACCEL1 项目,以克服这三个挑战,以实现 TCI 的实际应用。 我们研究了用于向堆叠芯片传输功率的高掺杂硅通孔 (HDSV) 和使用 TCI 促进散热的 2.5D 芯片中介层,都取得了令人鼓舞的结果。 初步测试结果也没有发现对 DRAM 操作的干扰。

与芯片相比,由于互连的分布式特性,具有较大物理尺寸的模块可以使用电磁耦合更优化地互连。 Transmission Line Coupler(TLC,传输线耦合)就是这样一种技术,它使用传输线构建耦合器,使用非广播无线电波将模块连接在一起。

ACCEL 项目的目标是证明使用 TCI 构建可实现 100 GFLOPS/W 功率效率的移动超级计算机的可行性。 为此,我们实施了一个堆叠式 DRAM 接口,在 0.5 pJ/bit 时实现了 512 GB/s 的数据速率,与当前最新的接口技术相比,数据速率提高了 30 倍,功率效率提高了 20 倍 。 此外,我们使用 TLC 将传感器和执行器等设备连接到乐高积木等移动超级计算机中,以支持其他功能。

TCI 在第 2 章详细讨论,TLC 在第 3 章详细讨论。我们对移动超级计算机的愿景在第 4 章介绍。

ENIAC 采用有线逻辑架构,其中编程是通过改变处理元件之间的物理连接来完成的。 很容易看出这种方法的可扩展性有限,因为最大可能程序的大小受到构建时放入系统中的处理硬件数量的限制。

为了克服这个限制,存储程序计算机应运而生。 在存储程序计算机中,处理和移动数据的命令以及要处理的数据首先存储在内存中。 然后处理器检索命令和数据、解释命令并处理数据。 与需要多个处理元件的物理连接的有线逻辑计算机不同,存储程序计算机只需要一个处理单元,该处理单元在每个时钟周期执行不同的命令。 它被誉为解决了可扩展性问题的革命性范式转变。

现代存储程序计算机的处理效率受到数据在内存和处理器之间移动的顺畅程度的限制。 这个问题被称为冯诺依曼瓶颈。 TCI 是一种无线 IC 接口技术,可以消除冯·诺依曼瓶颈,实现计算机处理效率的飞跃。

虽然 TCI 的创建是为了解决存储程序计算机的冯诺依曼瓶颈,但我们相信它还将使有线逻辑架构能够推动计算机技术的创新发展。

在有线逻辑计算机中,处理发生在数据流经大量不同处理硬件资源的过程中。 因此,定义硬件配置所需的信息量比存储程序计算机中使用的命令大几个数量级。 如果我们可以将这些信息存储在大容量内存中,并在需要以特定方式配置硬件时通过TCI接口即时检索必要的硬件定义信息,我们实际上可以瞬间创建一个虚拟的有线逻辑计算机 针对手头的特定信息处理任务进行了优化。

集成电路的性能演进路标

我们在 ACCEL 项目中开发的 512 GB/s 堆栈 DRAM 接口使我们能够消除内存访问中的 von Neumann 瓶颈,以支持有线逻辑计算机中大规模处理硬件的重新配置,从而实现实时虚拟化, 从而克服可扩展性问题,使我们能够利用有线逻辑架构的多样化和大规模处理资源。

人们可以将这一新颖的想法视为从 3D 到四维 (4D) 集成的演变,其中物理空间中的 3D 集成解决了互连处理器和存储芯片以形成硬件系统以及此类系统的多个变体的挑战性问题 通过重新配置来实现,并沿着作为第四维度的时间轴虚拟集成,从而产生 4D 集成。

在存储程序计算机中,处理功能首先映射为低级命令,然后顺序执行命令完成处理。因此,它最适合具有深度处理序列的过程信息处理,例如 电磁模拟。 另一方面,在虚拟有线逻辑计算机中,每个处理功能首先映射到可用处理资源的结构空间,然后处理数据并将其从一个虚拟配置传递到另一个虚拟配置以完成处理。 因此,它最适合具有大量数据流的结构化处理,例如深度神经网络 (DNN) 处理。 如果我们要将这些用于信息处理的计算机映射到大脑,前者将映射到左脑,后者将映射到右脑。

我们的下一个目标是探索一种新的信息处理范式,如下所示。 我们计划使用TCI 3D IC集成构建一个存储程序计算机作为左脑,以消除冯·诺依曼瓶颈,从而使电子左脑发挥其全部处理潜能。 同时,我们将使用 TCI 4D 集成构建一个虚拟有线逻辑计算机作为右脑,这也是通过消除冯诺依曼瓶颈而实现的。 然后我们将使用 TLC 将两者和其他构建模块(包括传感器和执行器)互连起来,以创建一个新的人工智能计算机,一个超越人脑性能的电子大脑,为信息处理开辟新的可能性。

0条评论