《半导体干法刻蚀技术(Dry Etching Technology for Semiconductors)》书籍介绍

《半导体干法刻蚀技术》

本书是半导体干法蚀刻技术的必备参考书,它将使工程师能够开发新的刻蚀工艺,以进一步实现半导体集成电路的小型化和集成化。作者描述了器件制造工艺流程,并解释了实际使用的流动干法蚀刻的基本原理。该内容旨在为在芯片制造商、设备供应商和材料供应商工作的工程师以及研究等离子体的大学生提供实用指南,重点关注他们最需要的主题,例如半导体器件中使用的每种材料(Si、SiO2、金属等)的详细蚀刻工艺,制造晶圆厂中使用的蚀刻设备,解释为什么使用特定的等离子体源和气体化学来蚀刻每种材料, 以及如何开发蚀刻工艺。本书还描述了最新的关键技术,如3D IC蚀刻,双大马士革蚀刻,低k刻蚀,Hi-k/金属栅极蚀刻,鳍式场效应晶体管刻蚀,双图案等。

《半导体干法刻蚀技术(Dry Etching Technology for Semiconductors)》的主要内容

作为微缩和提高半导体器件集成度的手段,干法刻蚀是一项与光刻技术重要性相当的关键技术。 从事干法刻蚀开发的工程师数量也与从事光刻技术的工程师不相上下。 光刻技术相对容易理解,因为其分辨率是由光学波长和透镜的数值孔径 (NA) 决定的。 另一方面,由于蚀刻室内发生的复杂现象,干法蚀刻技术很难理解。

干法蚀刻还需要电学、物理和化学方面的综合知识,因为基于等离子体的蚀刻是由物理化学反应驱动的。 从事干法蚀刻的工程师倾向于依靠他们的经验和直觉来进行工作。 很多时候,工程师们在没有充分了解和了解例如如何实现各向异性蚀刻、为什么 Cl2 和 HBr 用于硅蚀刻、为什么氟碳气体用于 SiO2 蚀刻,以及为什么使用电感耦合等离子体 (ICP) 等高密度等离子体来蚀刻多晶硅和铝,而使用中等密度等离子体的窄间隙平行板蚀刻机来蚀刻 SiO2 。 有时,即使是干法蚀刻专家也可能对这些问题了解不够透彻。

干法刻蚀技术有时可能会被光刻法黯然失色,但是,正如已经提到的,它是与光刻法一样重要的关键技术。 举例来说,在干法蚀刻中,(1)针对每种材料,例如Si、SiO2 和金属,使用特定的设备和工艺技术; (2)新技术不断开发,如Cu大马士革加工等新材料加工; (3) 带电粒子引起的等离子体损伤直接导致器件良率损失,需要了解其机理和解决方法; (4) 干法刻蚀比光刻技术更为关键,因为它决定了尺寸精度和均匀性。 从事这种工艺技术的工程师,为了支持更多的材料范围,这种工艺技术不断变得更加多样化和复杂化,应该对干法蚀刻技术有足够的了解。

本书采用不同于现有出版物的独特方法,帮助读者了解干法蚀刻的基础知识及其应用。 许多关于干法刻蚀的书籍都侧重于复杂的等离子体理论,或者只提供一长串与干法刻蚀相关的数据。 本书将尽可能避免使用数学方程式,旨在使干法蚀刻机制易于理解。 它还旨在让读者系统地了解工艺过程本身,然后了解设备和新技术。 有一章专门介绍等离子损伤,全面介绍了该主题。

本书不仅旨在帮助读者了解干法蚀刻的基础知识,还旨在帮助他们获得更多实用知识。 作者希望能为从事干法刻蚀开发的工程师提供一个指导原则。

干法刻蚀技术对半导体集成电路进步的贡献

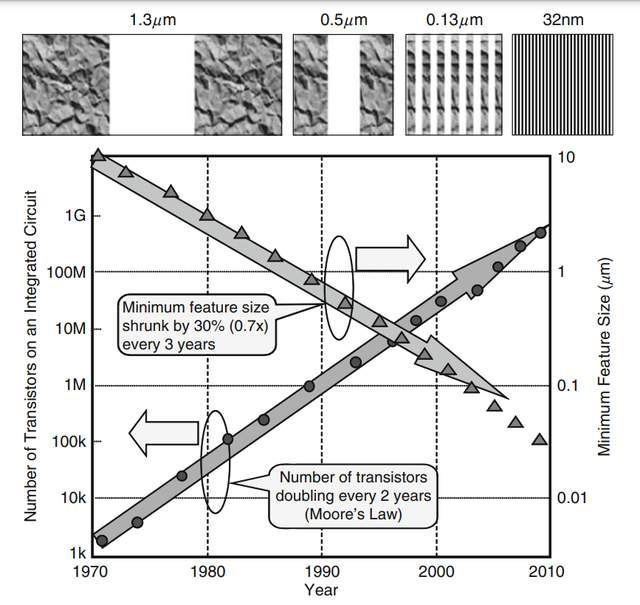

近年来计算机行业的进步,如多媒体设备等先进信息系统的快速商业化所见,是由各种大规模集成 (LSI) 设备(如微处理器和存储器)支撑的。 如图 1.1 所示,LSI 技术发展非常迅速,器件密度大约每 2 年翻一番。 图 1.1 中的晶体管数量指的是每个微处理器芯片上的晶体管数量,这种器件密度更高的趋势遵循摩尔定律。 最小特征尺寸每3年缩小约30%,20nm级最小特征尺寸的器件从2014年开始量产。

图 1.1 半导体集成电路的小型化和集成化趋势

更高的LSI器件密度意味着每个芯片内置的器件数量更多,关键是每个器件要尽可能小。 实现这一点的基础技术是精细几何加工,主要包括光刻技术和干法刻蚀技术。 光刻是一种在抗蚀剂上形成所需电路图案的技术,而抗蚀剂是一种感光材料。 干法蚀刻是一种将由抗蚀剂形成的电路图案转移到下面的薄膜上的技术,其方法是部分去除沉积在晶圆上的各种薄膜,并使用抗蚀剂作为掩模。 本章概述了干法蚀刻技术以及该制造工艺步骤在提高 LSI 器件密度方面的作用。

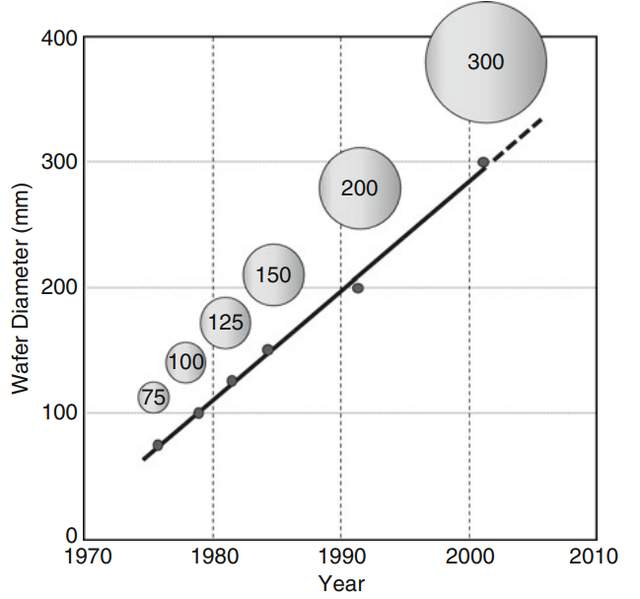

图 1.2 晶圆尺寸增长趋势

降低制造成本也是 LSI 制造的一个重要考虑因素。 如图 1.2 所示,已使用直径越来越大的晶圆来实现这一目标。 如图1.3所示,大量的LSI芯片形成在晶圆上。 他们的芯片图案是通过分步器在分步重复光刻工艺中在晶圆上创建的 。 当在制造工艺中使用更大的晶圆时,每个芯片的成本会下降,因为从每个晶圆中获得了更多的芯片。 目前制造中的最大晶圆直径为 300 毫米,接下来计划使用 450 毫米晶圆。 目前,450mm硅片已具备生产能力,450mm半导体设备包括干法刻蚀设备正在开发中。 正如迄今为止所解释的,器件缩放和更大的晶圆直径在半导体业务中是不可或缺的。 要实现这两个目标,就需要干法蚀刻技术创新。

图 1.3 在晶圆上形成的 LSI 芯片

干法刻蚀概述

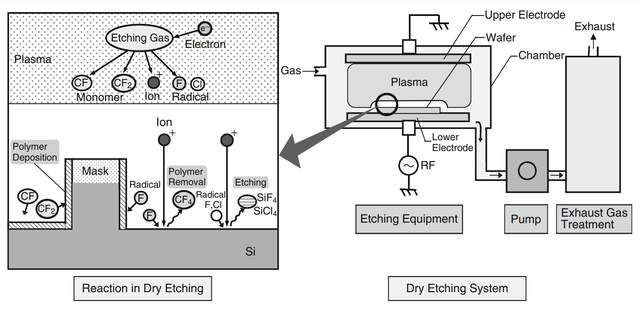

图 1.4 显示了干法蚀刻的概况。 我们将以平行板干法蚀刻系统为例进行讨论。 这种类型的蚀刻设备称为反应离子蚀刻 (RIE,reactive-ion etching)。 蚀刻室首先抽真空至高真空后,引入蚀刻气体。 接下来,当将 13.56 MHz 射频 (RF) 功率施加到一对彼此面对的电极时,就会产生等离子体。 蚀刻气体在该等离子体中解离,产生活性粒子物质,例如离子和自由基,以及构成聚合物基础的单体。

这些活性物质和单体被输送到晶圆表面并与蚀刻目标材料发生反应。 如图1.4左侧所示,晶圆附近发生了复杂的蚀刻和沉积竞争反应。 在此示例中,CF 和 CF2 单体形成聚合物并沉积在图案表面上。 这些聚合物与离子和 F自由基相互作用,并以 CF4 的形式剥离,而下面的 Si 通过与 F 和 Cl 自由基的相互作用而被蚀刻。 这些反应的副产物从晶圆表面解吸,蚀刻继续进行。 蚀刻副产品最终通过废气处理系统并排放到大气中。

图 1.4 干法刻蚀示意图

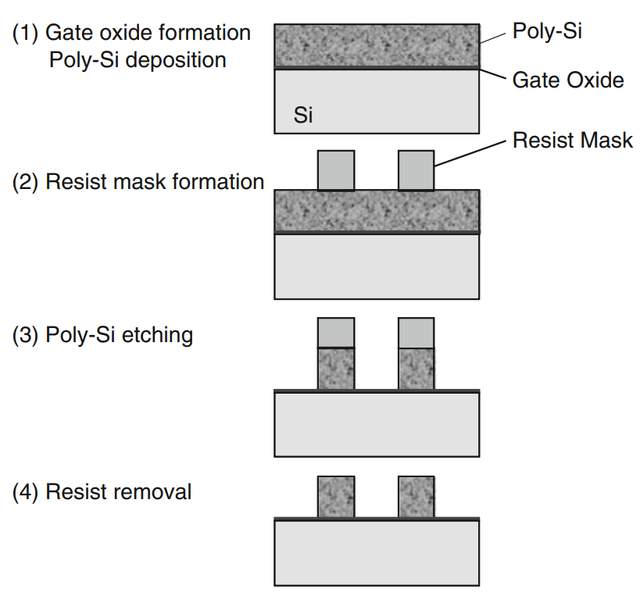

图 1.5 干法刻蚀工艺流程

图 1.5 显示了干法蚀刻工艺步骤流程。 以栅极刻蚀工艺为例; 此过程中涉及的步骤如下:

1.首先在Si衬底上形成栅氧化膜。 然后,作为栅极材料的多晶硅沉积在顶部。

2.接下来,通过光刻技术在抗蚀剂掩模上形成栅极图案。

3.将晶圆放入干法刻蚀设备中。 蚀刻下面的多晶硅,以抗蚀剂为掩模,当栅氧化膜暴露时蚀刻停止。

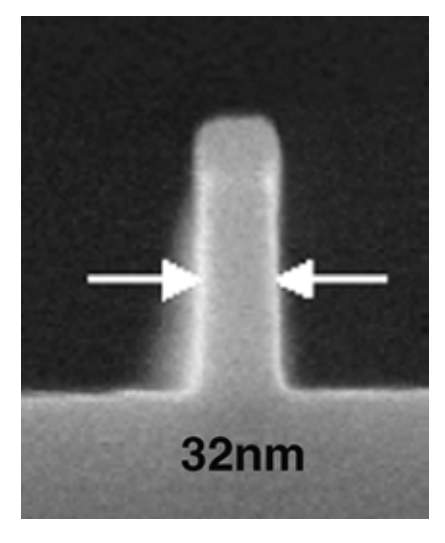

4. 剥离掉不再需要的抗蚀剂,完成多晶硅栅刻蚀。 图 1.6 显示了 32 纳米栅极蚀刻轮廓的 SEM 照片 。

图 1.6 32 纳米栅极的蚀刻轮廓示例

评价干法刻蚀性能的参数

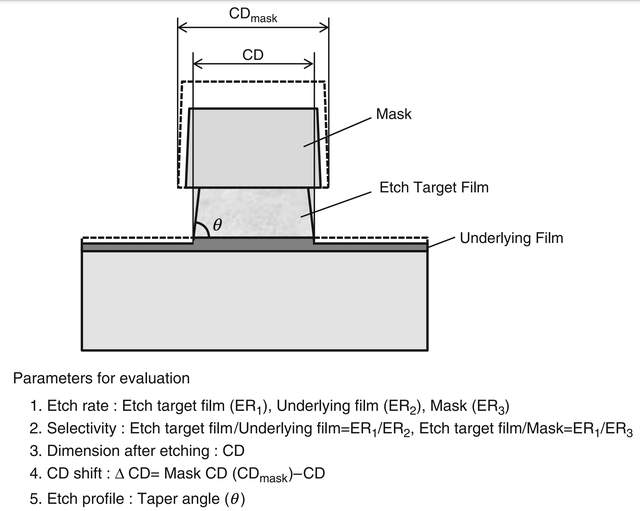

评价干蚀刻性能所需的参数如图 1.7 所示。 第一个参数是蚀刻速率。 蚀刻目标薄膜的蚀刻速率 (ER1,etch rate) 是根据蚀刻目标薄膜厚度和完全去除它的时间计算的。 ER1与产量直接相关,应选择工艺条件使其尽可能高。 底层膜的蚀刻速率(ER2)和掩模的蚀刻速率(ER3)是根据每个膜的蚀刻量计算的。

图 1.7 评价干法刻蚀性能的参数

刻蚀靶膜与底层膜的刻蚀速率比(ER1/ER2)和刻蚀靶膜与掩膜的刻蚀速率比(ER1/ER3)称为对底层膜的选择性, 分别表示对掩膜的选择性。 这些参数标识当蚀刻目标膜被蚀刻时底层膜和掩膜被蚀刻了多少。 对于干法蚀刻,总是需要过蚀刻,因为由于蚀刻速率不均匀和底层形貌,在终点处总是有蚀刻残留物。 更高的选择性意味着在过蚀刻过程中更少的底层薄膜被蚀刻掉,并且随着器件继续按比例缩小,需要更高的选择性。 例如,对于栅工艺,作为底层膜的栅氧化膜随着缩放而变薄。 如果没有高选择性,栅氧化膜很容易被蚀刻,结果会影响 LSI 的成品率。 为此,需要对下面的栅极氧化膜具有高选择性。 掩模的选择性也是如此。 较薄的抗蚀剂薄膜用于提高高度缩放设备上的光刻分辨率。 抗蚀剂的高选择性对于确保抗蚀剂在蚀刻过程中不被剥离是必要的。

临界尺寸(CD,critical dimension)是蚀刻完成后的成品尺寸。 CD是精细几何加工技术中最重要的参数。 例如,CD 对栅极工艺的晶体管性能有直接影响。 换句话说,CD决定了金属氧化物半导体(MOS)晶体管的阈值电压Vth。 当整个晶圆上的 CD 不均匀时,Vth 也会在整个晶圆上变得不均匀并导致良率损失。 因此,越来越需要具有更好均匀性的蚀刻。 下一节将更详细地讨论 MOS 晶体管。

与掩膜(CD 掩膜)上的临界尺寸的偏差量称为 CD 偏差 (ΔCD),定义为 ΔCD = CD 掩膜 – CD。

最后一个参数是蚀刻剖面。 理想情况下,垂直蚀刻剖面中的锥角 θ 应为 90°。 必须避免 θ 大于 90° 的倒锥形,因为它会在离子注入过程中产生阴影并对晶体管性能产生不利影响。 必须设置工艺条件以避免反向锥化。

干法刻蚀技术在LSI小型化和器件高密度化中的作用

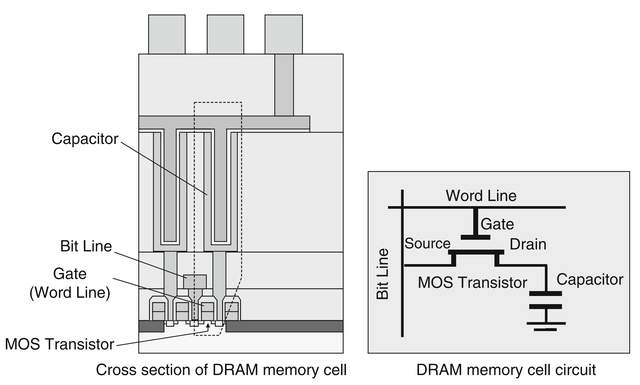

图 1.8 DRAM 内存单元结构

本节讨论干法蚀刻技术在 LSI 制造过程中的应用。 让我们以制造动态随机存取存储器 (DRAM) 设备为例。 图 1.8 显示了典型 DRAM 存储单元的横截面。 一个 DRAM 存储单元由一个 MOS 晶体管和一个电容器组成。 电路图显示在图 1.8 的右侧。 通过 MOS 晶体管的电子被储存在电容器中。 数据读取为“1”或“0”,分别取决于电容器是否充电。 图 1.9 显示了 DRAM 的制造工艺流程。

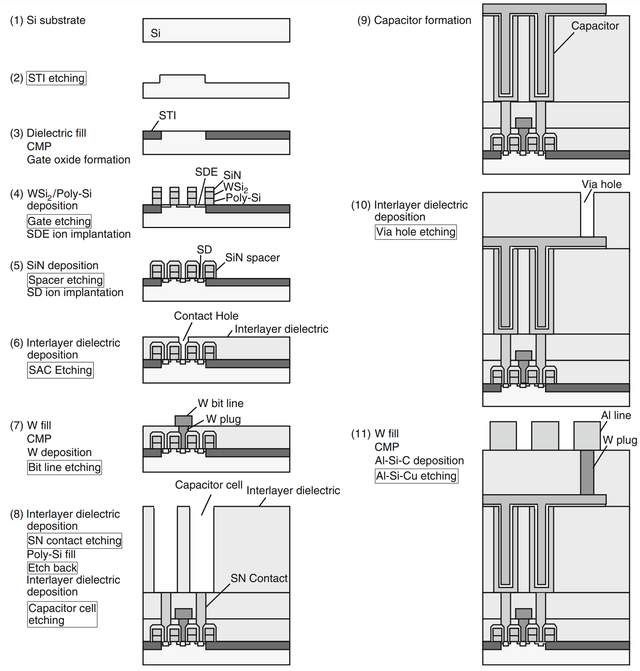

图 1.9 DRAM 制造工艺流程

详细工艺流程如下:

1.DRAM制造过程从裸硅衬底开始。

2.通过蚀刻Si衬底形成浅沟槽隔离(STI)。 此步骤称为 STI 蚀刻。 该图没有显示形成抗蚀剂掩模并在 STI 蚀刻后将其去除的步骤。 此外,用于形成和去除抗蚀剂掩模的步骤未包括在本说明书的其余部分中。

3. 接下来,用化学机械抛光(CMP)平坦化的绝缘膜填充STI沟槽。 这样就形成了隔离器件的隔离区。 然后形成栅氧化膜。

4.Poly–Si、WSi 2 和 SiN 沉积在栅氧化膜的顶部。 通过栅极刻蚀形成SiN/WSi 2 /多晶硅栅极结构。 然后通过离子注入形成源漏延伸(SDE)区。

5.接下来,将 SiN 沉积在栅极顶部,然后进行各向异性干法蚀刻。 因为SiN膜在垂直方向上较厚,所以SiN没有被蚀刻掉而保留在栅极侧壁上并形成间隔件。 该步骤称为间隔物蚀刻。 然后,进行源漏(SD)注入,形成源漏区。 现在形成了 MOS 晶体管。 MOS指的是金属(栅极金属材料,这里是WSi 2 /poly-Si)、氧化物(这里是栅极氧化膜)、半导体(这里是Si衬底)。 MOS晶体管的源极和漏极之间的电流通过施加在栅极上的电压来控制。 本书中所有“晶体管”均指“MOS晶体管”。

6.在沉积层间绝缘膜之后,通过自对准接触(SAC)蚀刻打开到Si衬底的接触孔。 由于栅极覆盖有作为蚀刻停止层的Si3N4 膜,所以即使存在未对准,接触孔和栅极也不会短路。 该技术在本书的第 3 章中有更详细的描述。

7.接下来,用钨 (W) 填充接触孔并通过 CMP 进行平坦化。 它们被称为钨塞。 然后将钨沉积在顶部并蚀刻以形成位线。

8. 沉积层间绝缘膜,然后进行存储节点 (SN) 接触蚀刻。 这里也使用了SAC蚀刻工艺。 存储节点触点填充有多晶硅并回蚀以进行平面化。 接下来,沉积厚的层间绝缘膜,然后进行单元蚀刻。 单元蚀刻是用于形成电容器的孔蚀刻步骤,并且由于非常高的纵横比(深度/孔直径)而极具挑战性。 高纵横比孔蚀刻在第 3 章中有详细描述。

9. 将电容器下电极(通常为多晶硅)、电容器绝缘膜和电容器上电极(通常为TiN)填充到单元中,这样就形成了电容器。

10、沉积层间绝缘膜后,刻蚀连接电容和金属线的过孔。

11.过孔填充W,CMP平面化。 接下来,沉积并蚀刻Al-Si-Cu,形成Al金属线。 DRAM 存储单元现已完成。

如上所述,通过重复沉积和干法蚀刻步骤创建LSI器件。 因此,刻蚀加工精度将极大地决定器件的性能和成品率。 虽然图 1.9 仅显示了简化的 DRAM 制造步骤,但它仍然说明了干法蚀刻技术在 LSI 制造过程中的重要作用。 本工艺流程中提到的每个干法蚀刻工艺在第 3章中有更详细的描述。