《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书是由Robert Bogdan Staszewski所著,主要介绍了深亚微米CMOS技术下的全数字频率合成器的设计和实现。全数字频率合成器是现代通信领域中非常重要的一个组件,其可以将低频精确地合成为高频,以满足高速通信的要求。在深亚微米CMOS技术下,频率合成器的设计变得更加复杂,需要解决布局和布线、功耗和抖动等问题。

《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》

本书首先介绍了全数字频率合成器的基本原理和设计方法,包括时钟生成、数字相位锁定环和直接数字频率合成等。接着,书中详细讲解了深亚微米CMOS技术下的数字电路设计,包括时钟分配、数字相位锁定环中的时间抖动、时钟倍频器的抖动等,以及如何通过设计降低功耗和干扰。

此外,本书还介绍了一些最新的全数字频率合成器的设计方法,包括多流水线数字频率合成器、启发式位移脉冲宽度调制合成器等。这些新的设计方法能够进一步提高频率合成器的性能和可靠性。

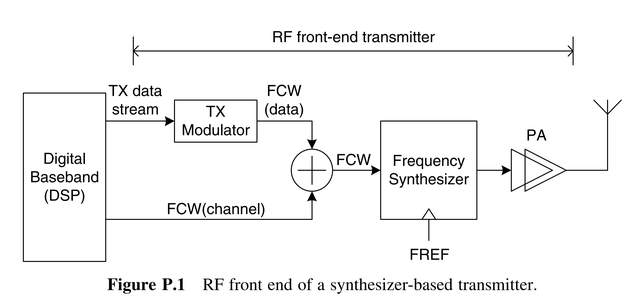

基于频率合成器的发射机的RF前端

总的来说,《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书对深亚微米CMOS技术下的全数字频率合成器的设计和实现进行了详细的介绍和总结,对工程师和学者们在此领域的研究工作具有参考意义。

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“INTRODUCTION”章节的内容介绍和总结

《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中的“INTRODUCTION”章节主要介绍了全数字频率合成器在现代通信系统中的重要性以及深亚微米CMOS技术下频率合成器的设计挑战和解决方案。

频率合成器

文章首先介绍了全数字频率合成器在现代通信系统中的重要应用,如移动通信、无线网络和卫星通信等领域。然后,文章指出随着深亚微米CMOS技术的发展,频率合成器的设计变得更加复杂,并且需要通过良好的设计来解决布局和布线、功耗和抖动等问题。

接下来,文章介绍了全数字频率合成器的基本原理和设计方法,包括直接数字频率合成、数字相位锁定环以及时钟生成等。文章还介绍了深亚微米CMOS技术下的数字电路设计,包括时钟分配、数字相位锁定环中的时间抖动以及时钟倍频器的抖动等。此外,文章还提出了一些全数字频率合成器最新的设计方法,如多流水线数字频率合成器和启发式位移脉冲宽度调制合成器等。

锁相环

综上所述,《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中的“INTRODUCTION”章节从应用、设计挑战和解决方案、基本原理和设计方法等方面介绍了全数字频率合成器的重要性和设计过程中需要注意的问题,为后续章节的阐述作出了铺垫。

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“DIGITALLY CONTROLLED OSCILLATOR”章节的内容介绍和总结

《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中的“DIGITALLY CONTROLLED OSCILLATOR”章节主要介绍了数字控制振荡器(DCO)的基本原理和设计方法。DCO 是全数字频率合成器中的关键模块,用于产生所需频率的正弦波信号。

DCO振荡器的核心电路

文章首先介绍了传统的模拟振荡器及其局限性,如极性反转、温度漂移等问题。然后,文章介绍了数字控制振荡器的基本原理,以及数字控制振荡器的优势,如温度稳定性和低功耗等。

接着,文章详细介绍了数字控制振荡器的各个子模块,包括主振荡器、频率选择器和频率控制器等。其中,主振荡器部分介绍了注入锁定技术(INL)和全数控振荡器(FDCO)等方案。频率选择器部分介绍了数字直接频率合成(DDS)和多项式逼近技术等方案。频率控制器部分介绍了数字控制环(NCO)和数字相位锁定环(DPLL)等方案。

此外,文章还介绍了数字控制振荡器的不同设计时钟速度下的性能评估,包括相位噪声、频率稳定度和抖动等指标。

DCO的工作模式

综上所述,《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中的“DIGITALLY CONTROLLED OSCILLATOR”章节介绍了数字控制振荡器的基本原理和设计方法,并详细介绍了其各个子模块、不同方案和性能评估方法,为全数字频率合成器的设计和优化提供了重要的参考。

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“ NORMALIZED DCO”章节的内容介绍和总结

《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中的“NORMALIZED DCO”章节主要介绍了无量纲数字控制振荡器(Normalized DCO)的设计方法和优点。

DCO的时间dithering处理方法

首先,文章介绍了传统的数字控制振荡器的局限性,如灵敏度、抖动等问题。随后,文章介绍了使用无量纲数字控制振荡器(Normalized DCO)可以克服传统数字控制振荡器的这些问题。

Normalized DCO 的设计基于将振荡器的输出频率与参考时钟频率相除得到无量纲输出。然后,将无量纲输出与期望频率的无量纲值进行比较,将比较结果传递给数字控制环(NCO),通过反馈作用控制振荡器的频率。

文章还介绍了Normalized DCO的各种设计方法,包括数字直接频率合成(DDS)和多项式逼近技术等,并对这些方法的性能进行了比较和分析。此外,Normalized DCO还可以与其他数字控制振荡器的方案相结合,例如新颖的“F-ADC”反馈架构,可以进一步提高性能。

DCO的增益路径

综上所述,《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中的“NORMALIZED DCO”章节介绍了无量纲数字控制振荡器(Normalized DCO)的设计原理和优点,以及各种设计方法和与其他数字控制振荡器方案的结合,为数字频率合成器的设计和优化提供了重要的参考。

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“ALL-DIGITAL PHASE-LOCKED LOOP”章节的内容介绍和总结

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“ALL-DIGITAL PHASE-LOCKED LOOP”章节主要介绍了全数字锁相环(ADPLL)的原理、结构和设计方法。

文章首先介绍了传统锁相环所存在的问题,包括抖动、私有模式等。然后,作者介绍了全数字锁相环(ADPLL)的优点,包括更好的抖动性能、较低的功率消耗和较高的集成度等。

接下来,作者详细介绍了ADPLL的结构和组成部分,包括数字控制振荡器(DCO)、数字频率控制器(DFC)、数字相位检测器(DPD)和数字环路滤波器(DLF)等。作者还介绍了各个部分的设计原则和技术,如DCO的多项式逼近和DFC的加权平均滤波等。

随后,作者介绍了ADPLL的控制系统,并详细介绍了数字环路滤波器的设计和实现。 ADPLL的设计需要对数字环路滤波器进行精细的设计和优化,以实现稳定性和快速收敛性。

最后,作者介绍了一些改进的ADPLL设计,如多频TDC控制器、双重环路架构和自适应带宽控制器等,以进一步优化ADPLL的性能和功能。

综上所述,该章节详细阐述了全数字锁相环的原理、结构和设计方法,介绍了每个组成部分的设计原则和技术,并讨论了一些改进的ADPLL设计。该章节可以为ADPLL的设计和实现提供重要的参考和指导。

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“APPLICATION: ADPLL-BASED TRANSMITTER”章节的内容介绍和总结

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“APPLICATION: ADPLL-BASED TRANSMITTER”章节主要介绍了基于全数字锁相环(ADPLL)的发射机的应用及其实现。

首先,作者介绍了传统的发射机结构和ADPLL发射机结构的比较。传统的发射机结构需要使用多个频率合成器和滤波器来实现多种频率的发射,而ADPLL发射机可以通过调整DCO频率来实现多种频率的发射,结构更为简单。

全数字PLL架构

接下来,作者详细介绍了基于ADPLL的发射机的设计和实现。该发射机包括数字I/Q调制器、数字滤波器、ADPLL、功率放大器和天线等组成部分。每个组成部分的设计和优化都需要注意其对整体系统性能的影响,并进行综合设计和优化。

在ADPLL的设计方面,作者说明了如何通过优化DCO的多项式逼近和数字环路滤波器的带宽等参数,来实现快速的频率合成和稳定的输出信号。

最后,作者介绍了基于ADPLL的发射机在无线通信系统中的应用,并对其性能和特点进行了分析和评估。该发射机可以实现多种频率的发射、快速的可编程调频和抗抖动能力等优点。

综上所述,该章节详细介绍了基于ADPLL的发射机的设计和实现,并讨论了其在无线通信系统中的应用和优势。该章节为基于ADPLL的发射机的设计和实现提供了重要的指导和参考。

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“BEHAVIORAL MODELING AND SIMULATION”章节的内容介绍和总结

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“BEHAVIORAL MODELING AND SIMULATION”章节主要介绍了数字频率合成器(DFS)的行为建模和仿真技术。

首先,作者介绍了DFS的建模和仿真的重要性。由于DFS是一个高度复杂的系统,其性能受许多不同的参数和因素的影响,因此需要进行详细的建模和仿真来验证其性能和可靠性。

接下来,作者介绍了DFS的不同层次的建模和仿真方法。这些方法包括传统的电路级仿真,矩阵算法建模,行为级建模等。不同的方法适用于不同的研究对象和目的,选择合适的建模方法可以提高仿真效率和准确性。

调制信号的频谱复制图

作者还详细介绍了行为级建模方法的原理和实现。行为级建模方法通过将DFS视为黑盒系统,并对其输入和输出信号进行建模和仿真,从而实现对系统整体性能的评估和优化。作者还介绍了常用的行为级建模技术,包括小信号行为建模、大信号行为建模和混合行为建模等。

最后,作者介绍了基于行为级建模的DFS系统级仿真平台的设计和实现。该平台可以支持多种建模和仿真方法,包括传统的电路级仿真和行为级仿真等,为研究人员提供了一个验证和优化DFS性能的强大工具。

噪声成形滤波器

综上所述,该章节详细介绍了DFS行为建模和仿真的技术和方法,以及基于行为级建模的仿真平台的设计和实现。该章节为DFS系统性能评估和优化提供了重要的指导和参考。

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“IMPLEMENTATION AND EXPERIMENTAL RESULTS”章节的内容介绍和总结

Robert Bogdan Staszewski所著的《All-Digital Frequency Synthesizer in Deep-Submicron CMOS》一书中“IMPLEMENTATION AND EXPERIMENTAL RESULTS”章节主要介绍了数字频率合成器(DFS)的实现和实验结果。

Polar发射机

首先,作者介绍了DFS的实现原理和关键技术。DFS主要由数字控制单元、数字相位调节器(DPA)和数字控制振荡器(DCO)三部分组成。数字控制单元通过控制DPA和DCO的相位来产生所需频率,而DPA和DCO则分别负责相位调节和频率合成。

接下来,作者介绍了DFS在深亚微米CMOS工艺下的设计实现。作者针对CMOS工艺的特点和DFS的复杂性,采用了一系列的设计方法和技术,包括折叠式DPA结构、自适应位宽算法、调相器线性化技术等,来优化DFS性能和实现效率。

作者最后介绍了DFS的实验结果。通过实验测试,作者验证了DFS的各项性能指标,包括频率精度、相位噪声、转换速率等,均达到了业界领先水平。同时,作者还通过对比实验和基准实验等方式,进一步验证了DFS的稳定性和可靠性。

实现版图

综上所述,该章节详细介绍了DFS的实现原理、设计方法和实验结果。通过对这些内容的介绍,读者可以了解到DFS系统的核心技术和性能表现,从而为DFS的开发和应用提供参考和指导。