题记

封装测试(PT,packaging and testing )产业在IC产业链中不可或缺。 近年来,在《国家集成电路产业振兴纲要》和《国家集成电路产业投资基金》的推动下,我国PT产业发展迅速。 传统上,封装的功能包括支持IC的机械保护、电信号传输、功率分配和热管理等。 随着IC技术的发展,IC封装在多种功能集成和复杂系统级封装(SiP)测试方面发挥着新的作用。 随着先进封装技术的发展,晶圆级封装(WLP)、系统级封装(SiP)、三维(3D)封装等迅速兴起,朝着电子系统进一步小型化和可靠性增强的方向发展。 在国家重大科技专项的持续支持下,封装测试能力和技术水平显著提升,向整个集成电路产业的高端产品迈进。 通过阅读本文和推荐的书籍,读者将系统地了解封装测试行业的现状、传统封装技术和先进封装技术的关键流程,并深入了解封装测试、可靠性等方面的知识。

IC 封装在超摩尔时代扮演着越来越重要的角色。 引线键合、倒装芯片和硅通孔 (TSV) 是 20 世纪 60 年代以来的主流互连技术。 系统级封装 (SiP) 于 2000 年代初期提出,并在业界逐渐流行。 过去15年,我国的封装测试(PT)行业发展非常迅速。 协同创新有多种,如产学研合作新模式、集成电路封装测试战略联盟、成立技术研究中心等,PT产业迅速壮大,并逐渐与前沿技术接轨。 据CSIA统计,封测收入约占我国整个半导体行业的三分之一。 全球PT行业主要有两种商业模式。 一种是隶属于集成器件制造商(IDM)的PT工厂,另一种是独立的PT工厂,也称为外包半导体组装和测试(OSAT,Outsourced Semiconductor Assembly and Testing)。 在我国,一些大学和研究机构正在研究封装技术,为行业推广做出贡献。

优质的学习资源中心cloudioe:关注我们,持久地阅读学习,投资您自己、提升您的能力和格局,改变您的生活!我们也能帮公司企业和研发人员吸收宇宙的力量,提高研发效率,降低研发投资,找到应用灵感!

全球IC PT(封装测试,封装测试)产业的发展综述

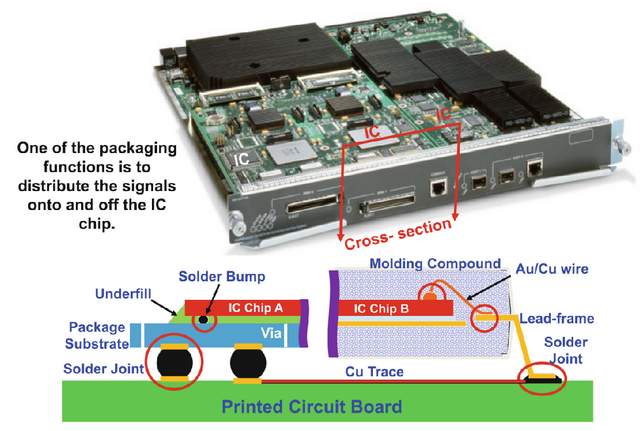

图1. 电子产品内部和典型 PCB 横截面示意图

作为集成电路(IC)产业中不可或缺的环节,IC封装(或装配)和封装测试(packaging and testing,PT)产业随着IC技术的进步而不断进步。 传统上,封装用于支持IC(例如机械保护、电信号的互连和提取、配电和热管理等); 随着系统集成硅技术的发展,封装还提供了新的功能。 从封装类型来看,早期的封装技术主要有金属晶体管外形(TO,Transistor Outline)封装和陶瓷双列直插式封装(CDIP,Ceramic Dual-In-line Package),均属于引脚通孔(PTH,Pin-Through-Hole)封装类型。 对于先进的IC技术来说,需要更高的封装密度,从而导致更多封装类型的开发。

自20世纪90年代初以来,双列直插式通孔封装逐渐转向表面贴装封装类型。 典型的封装类型包括小外形封装 (SOP)、四方扁平封装 (QFP)、球栅阵列 (BGA) 封装等。 随着先进技术的发展,最近出现了晶圆级封装(WLP)、三维封装(3DP)和系统级封装(SiP)。 封装类型和技术之间的区别越来越模糊。 根据芯片与封装之间的互连方式,通常称为引线键合(WB,)、卷带自动键合(TAB)、倒装芯片(FC)和硅通孔(TSV)技术等等。

传统封装技术主要利用引线框架作为载体和引线键合进行互连(例如 DIP、SOP 和 QFP) ); 随后出现了引线键合互连与封装基板的结合(例如BGA、Land Grid Array(LGA)等); 后来又实现了封装基板上的倒装芯片技术(例如Flip-chip-BGA)。

国际半导体技术路线图(ITRS)明确提出了未来IC技术发展的两个方向:More Moore(摩尔定律的延续)和More-than-Moore(超越摩尔定律)。 沿着More-than-Moore的技术路线,SiP中多种功能IC的集成越来越受到关注,包括信息处理芯片(例如中央处理单元(CPU)、微控制单元(MCU)、存储器以及信息交互芯片(例如射频IC、传感器等)等。 因此,系统级封装(SiP)已成为系统集成的主流技术路径之一。

据最新统计,2016年全球封装测试(PT)行业总收入约为500亿美元。IC Insights估计,PT行业(也称外包组装与测试,OSAT)收入占全球IC总收入总量的55%, 这本质上反映了全球PT产业规模及其在IC产业链中的比重。 目前,在全球PT行业中,我国台湾地区的企业处于领先地位,而我国大陆地区的企业也取得了显著的进步。

5G 封装技术对于5G系统的重要性简述

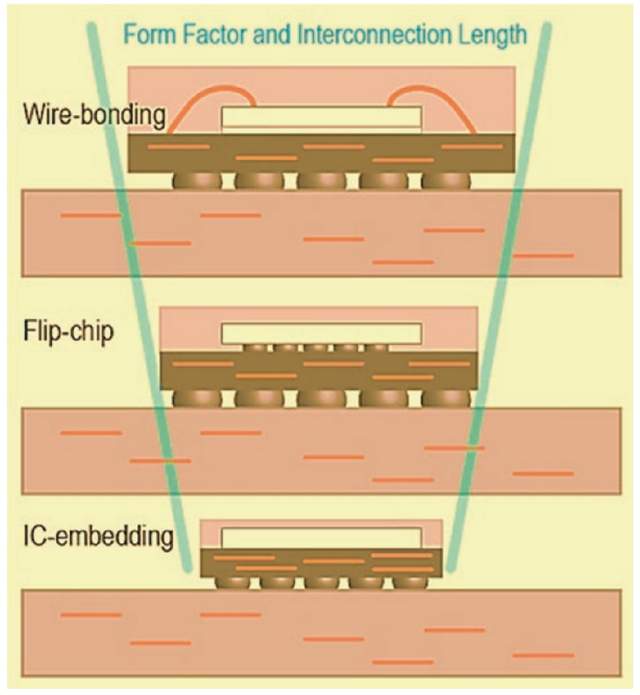

图2. 射频/毫米波技术小型化互连组装方法的趋势。

图2. 射频/毫米波技术小型化互连组装方法的趋势。 引线键合作为最传统的低 I/O 互连、低至 25 μm 的 FIP 芯片互连以及 IC 嵌入(IC-embedding)或扇出互连(fan-out interconnection);

5G 系统的电子封装需要将射频、模拟和数字功能以及无源器件和其他系统组件集成在单个模块中。 这些系统完美地体现了异质集成的趋势。 由于以下几个原因,使得异质集成对于 5G 系统变得更加重要了:

(a)天线与收发信机芯片(ICs)以及相关的无源和 RF 功率分配器网络的集成;

(b)随着封装技术的进步,短期内会增加 6 GHz 以下 (FR1) 的功能;

(c) 新的毫米波段(FR2)推动了新型滤波器和双工器以及宽带功率放大器和开关的集成;

(d) 现有 RFFE(射频前端) 的附加模块更加强调小型化和组件集成。

收发信机和前端模块的接近程度对于减小尺寸和损耗也很重要。 这是通过将天线与射频模块集成以及散热解决方案的同步建模以将有源组件保持在可接受的热耗条件下来实现的。 功率放大器与天线阵列的集成需要解决尺寸、成本和性能方面的挑战。 这些挑战转化为具有细线特征和精确的层间配准的多层制造、可减少传导损耗的先进低损耗材料以及电路、器件、封装和热解决方案的协同仿真。 新兴的 3D 封装集成解决方案还强调了各个电路块之间隔离的必要性。

另外,由于在数百万个基站中部署了此类高功率放大器和大型天线阵列,因此需要解决大批量制造的成本问题。

毫米波技术的系统级封装分为基带模块和天线集成收发信机模块。 在此类封装中,IC与其他元件(例如天线、无源元件和PCB)之间的互连必须满足多项要求。 最关键的要求之一是阻抗控制,尤其是在模拟领域。 在毫米波天线封装 (AiP) 解决方案中,收发信机 IC 和天线之间的互连应在感兴趣的频率范围内实现低插入损耗和可接受的回波损耗(VSWR)。 另一个关键要求是与互连技术相关的外形尺寸。 如图2 所示,两种传统互连技术是引线键合技术和 fip-chip 芯片互连技术,而新兴技术称为IC嵌入(IC embedding)或者扇出封装(fan-out packaging)。 尽管fip-chip 芯片和扇出互连最初是为高性能计算 (HPC) 或者移动处理器()应用而开发的,但它们的互连属性(例如细间距和低电气寄生效应)在 RF/毫米波封装中变得至关重要,例如 作为基带模块和天线集成模块。

5G 系统的封装要求

图3. 系统集成毫米波封装示例: (a) 调制解调器 SoP; (b) 天线集成封装;

尽管封装行业已经成熟并具有成本效益,但由于键合线会导致显著的信号损失和阻抗不连续性,因此使用引线键合技术进行互连已被认为是系统级封装 (SoP,system-on-package) 的关键挑战之一 ,这会降低射频/毫米波系统链的性能。 使用 fip-chip 芯片技术的互连比引线键合具有更好的性能,因为凸块高度小于键合线的长度。 fip-chip 芯片技术也更适合小外形尺寸,可提供 800 多个输入/输出 (I/O)。 fip-chip 芯片技术始于直径范围为 75-200 μm 的焊料凸块,而带有焊料帽的铜柱互连目前直径已达到小于 40 μm。 铜柱技术不仅提供高密度 I/O,而且还提供更低的传导损耗。 IC 嵌入(IC-embedding)或者扇出封装(fan-out packaging)的发展势在必行。

嵌入式晶圆级球栅阵列 (eWLB) 和扇出晶圆级封装 (FOWLP) 作为毫米波封装而备受关注。 这种嵌入技术消除了引线键合的使用,引线键合不仅会带来显著的高频损耗和寄生效应,而且还会增加高引脚数芯片的占地面积。 收发信机 IC 通过压缩成型工艺嵌入到重新配置的模制晶圆中。 形成多个重新分布层(RDL,Multiple redistribution layers)以扇出基带信号,并利用穿模通孔(through-mold vias)进行垂直互连。 与基于模塑料的波片级 IC 嵌入技术相结合,基于层压板和玻璃的面板级嵌入技术也正在成为替代候选技术。

图 3说明了5G系统关键的调制解调器和天线集成封装。 大多数情况是这样的模块采用三种互连方法中的多种技术的组合。 键合线可以充当 PCB 板和堆叠在逻辑或调制解调器芯片顶部的存储器之间的互连,而具有高引脚数的调制解调器芯片需要 FIP 芯片互连,以提供干净的信号并减轻信号延迟。 由于工艺成本和供应链成熟度,目前将毫米波相控天线阵列与互连 IC 集成的最流行的组装方法是 fip-chip 芯片技术。 导电材料选自铜柱或 C4(fip-chip)凸块(bumps),具体取决于引脚数和组装芯片对互连引起的导电损耗的敏感度。

与“封装技术”研究课题相关的参考学习书籍(下载地址www.cloudioe.com)

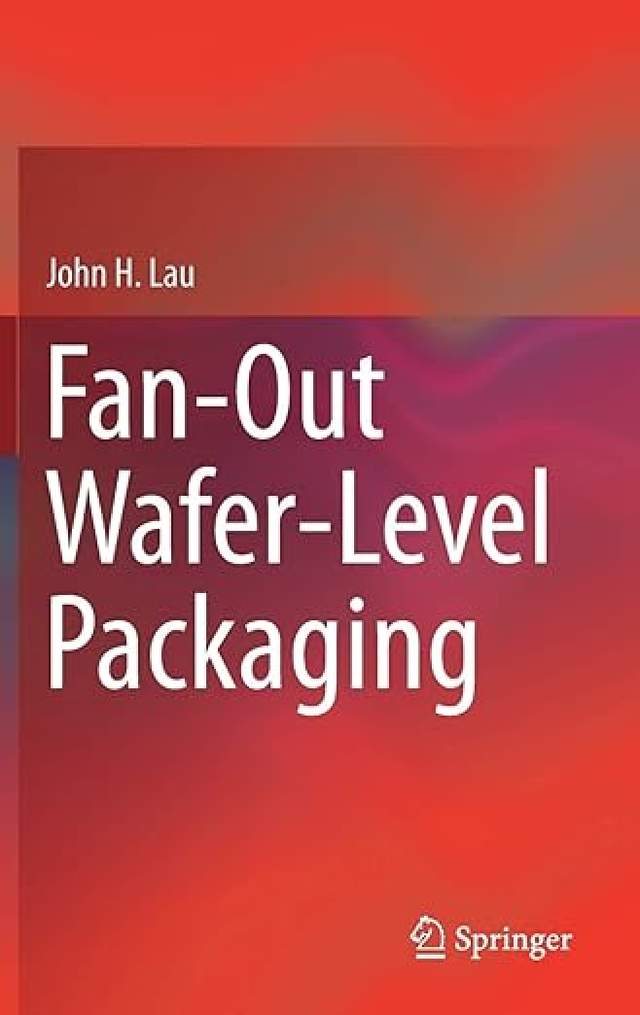

1.《扇出晶圆级封装(Fan-Out Wafer-Level Packaging)》

图5. 《扇出晶圆级封装(Fan-Out Wafer-Level Packaging)》

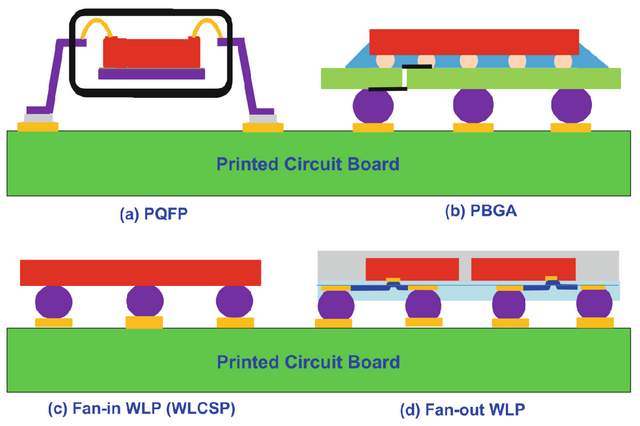

这本有关扇出晶圆级封装 (FOWLP,fan-out wafer-level packaging) 技术的综合指南将 FOWLP 与倒装芯片(flip chip)和扇入晶圆级封装(fan-in wafer-level packaging)进行了比较。 它介绍了有关 FOWLP 关键支持技术的当前知识,并讨论了几种未来趋势的封装技术。 台积电 (TSMC) 于 2016 年在苹果 iPhone 的应用处理器 A10 中采用了 InFO(集成扇出,integrated fan-out)技术,引起了整个半导体封装界对 FOWLP 技术的极大关注。 对于许多执业工程师和管理人员以及科学家和研究人员来说,FOWLP 的基本细节 – 例如重组晶圆/面板上载体的临时键合和脱键合(bonding and de-bonding )、环氧模塑料 (EMC,epoxy molding compound) 点胶、压缩成型、铜揭示(Cu revealing)、RDL 制造、焊球安装(solder ball mounting)等 -许多研发工程师和相关专业的学生尚不清楚。

图4. 示意性地显示了影响半导体封装的专利。a, 引线框架。 b, 基板和面阵焊球。 c, 扇入 WLP。 d, 扇出 WLP

本书旨在帮助读者学习解决问题方法的基础知识,并了解快速做出系统级决策所固有的权衡,对于所有面临因不断增长的兴趣而产生的挑战性问题的人来说,本书是一本有价值的参考指南。 FOWLP 有助于消除障碍,并加速 FOWLP 关键支持技术的设计、材料、工艺和制造开发。

本书共有11章,分别是(1)扇出晶圆级封装的专利问题、(2)倒装芯片技术与FOWLP、(3)扇入晶圆级封装与FOWLP、(4)嵌入式芯片封装,(5) FOWLP:芯片在前(Chip-First )和芯片朝下( Die Face-Down),(6) FOWLP:芯片在前和芯片朝上(Die Face-Up),(7) FOWLP:芯片在后或 RDL 在前,(8) FOWLP:PoP( (9) 扇出面板级封装 (FOPLP)、(10) 3D 集成和 (11) FOWLP 的 3D IC 异构集成。

本书所涉及到专业技术词汇:

- 3D IC Integration

- 60th Electronic Components

- application processor

- backgrinding

- Ball Grid Array

- C4 bumps

- Chen

- Chip Chip

- Chip Scale Package

- chip-first

- chip-last

- chipset

- Components and Technology

- compression molding

- contact pad

- corner solder joint

- crack length

- crack tip

- device wafer

- dielectric layer

- DRAM

- Electronic Packaging

- Embedded Wafer Level

- EMC

- EMIB

- etching

- eWLB

- fabricated

- face-up

- fan-in

- Fan-Out Wafer-Level Packaging

- flip chip

- flip chip assembly

- Flip Chip Technology

- FOPLP

- FPGA

- glass carrier

- GPU

- HBM

- heterogeneous integration

- IC packaging

- IEEE

- IEEE 60th Electronic

- IEEE/ECTC Proceedings

- IMAPS

- Interconnect

- J.H. Lau

- key process steps

- KGD

- KGD KGD

- laminate

- Lee

- LTHC

- Microbumps

- organic substrate

- outer crack

- panel

- Passivation

- Patent

- PCB

- photoresist

- pitch

- polymer

- PoP

- RDL-first

- RDL1

- RDL2

- RDL3

- RDLs

- reconstituted wafer

- Reliability

- semiconductor

- silicon

- SiO2

- smartphones

- solder balls

- solder bumps

- spin coating

- Stacked

- stencil

- TCB

- temperature

- test chip

- test package

- thermal cycling

- thickness

- TSMC

- UBM

- underfill

- wafer bumping

- warpage

- wire bonding

- WLCSP

- µm

2.《面阵互连手册(Area Array Interconnection Handbook)》

图6.《面阵互连手册(Area Array Interconnection Handbook)》

本手册在优化致密化、功能和可靠性方面对芯片和微电子封装的面阵互连进行了全面的分析和处理。 它提供了与替代技术和竞争技术的比较,明确定义了成本与收益的权衡和策略。 工艺细节按照其典型制造顺序的顺序定义,阐明工具要求和潜在的产量降低等因素之间的关系。 此外,该手册还有专门的章节专门介绍在满足微电子封装应用要求方面发挥关键作用的学科:包括高效散热技术、互连的冶金和机械特性以及电气设计策略等。

本书所涉及到专业技术词汇:

- adhesive

- alignment

- alloy

- applications

- area-array

- assembly

- attached

- Ball Grid Array

- BGA

- burn-in

- CBGA

- CBGA packages

- CCGA

- ceramic chip carriers

- chip carrier

- Chip Scale Package

- chip-carrier

- circuit

- components

- connector

- copper

- cost

- CSP

- CTE

- density

- device

- diameter

- dice

- dielectric

- electrical

- Electronic

- epoxy

- etching

- eutectic

- failure

- fatigue

- Fig

- film

- flex

- flip chip

- flip-chip solder

- flux

- heat

- IBM

- IEEE

- increase

- interconnection

- intermetallic

- JEDEC

- KGD

- laminate

- Land Grid Array

- laser

- layer

- manufacturing

- mask

- materials

- MCM

- mechanical

- metal

- method

- Microelectronics

- mils

- module

- oxide

- PBGA

- PCB

- performance

- pin

- pin grid array

- pitch

- placement

- plating

- polyimide

- probe

- Proc

- QFP

- reflow

- reliability

- removal

- resistance

- rework

- Schematic

- silicon

- socket

- sol

- solder balls

- solder bumps

- solder joints

- solder paste

- stencil

- strain

- stress

- structure

- substrate

- Surface Mount

- Table

- tape

- TBGA

- temperature

- thermal cycle

- thickness

- thin

- thin-film

- tion

- tool

- typically

- UBM

- underfill

- utilized

- wafer

- wire bond

- µm

《面阵互连手册(Area Array Interconnection Handbook)》一书的推荐说明

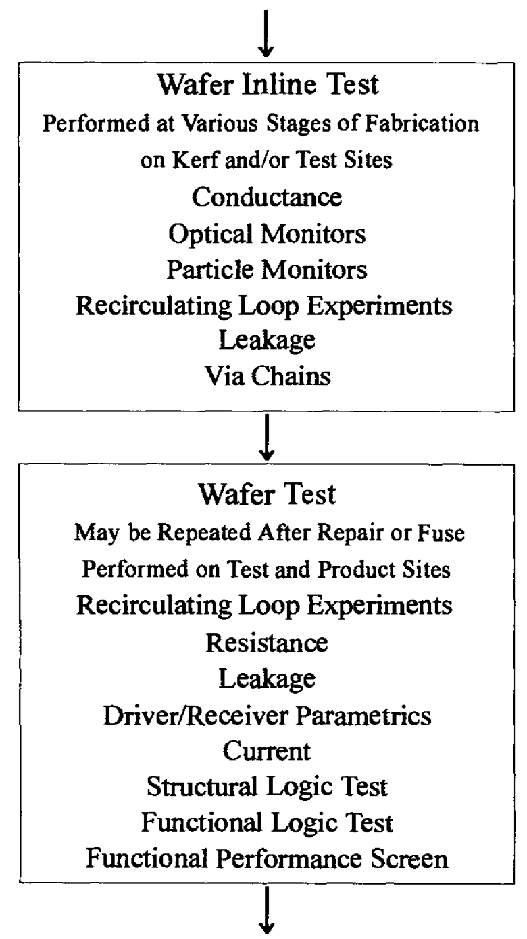

图4. Wafer (晶圆)测试流程;

微电子封装被认为是我们在二十世纪最后三十年见证的电子领域固态革命的重要“推动者”。 封装为晶体管和集成电路提供了必要的外部布线和互连能力,同时它们也经历了从分立器件到千兆级集成的壮观革命。

在 IBM,当需要更好的方法来提高半导体的可靠性和可制造性时,我们很自豪能够创建带有焊料凸块连接(solder bump connections)的倒装( flip chip )芯片的最初、简单的概念。 20 世纪 60 年代为 SLT(Solid Logic Technology,固体逻辑技术)选择的基本设计很容易扩展到 70 年代的集成电路以及 80 年代和 90 年代的 VLSI。 从最初的三个 I/O 凸块已增至 3000 个,预计未来还会有更多。

封装系列已从厚膜 (SLT) 发展到薄膜(金属化陶瓷)再到共烧多层陶瓷。 后来开发了具有与硅和铜内部布线相匹配的扩展性的陶瓷系列技术,它们被作为铜、多层、亚微米布线芯片互连革命的前身。 强大的服务器封装已经开发出来,其中组合的芯片和封装铜线超过一公里。 所有这一切都是通过通过短而高效的互连最大限度地减少电路延迟这一恒定目标来实现的。

倒装芯片还找到了借助减少倒装芯片和有机载体之间的底部填充应力的方式将芯片直接附着在印刷线路板和柔性电路上。 日本 IBM 开发的表面层状电路 (SLC,Surface Lamilar Circuit) 采用微孔技术,令电子商品领域兴奋不已,纷纷探索用于笔大小的寻呼机、微型电话、可穿戴 PC 和微型文件存储设备的倒装芯片设计。

硅芯片上面阵凸块(area array bumps)的成功应用无疑启发了后来在基板底部应用更大的焊料凸块(球栅阵列,ball grid arrays)。 这些球栅阵列进一步致密化并提高了卡和板之间的互连性能。 焊料凸块的衍生应用为表面贴装革命提供了又一个发展步骤,成为 20 世纪 80 年代及以后的首选卡和板技术(card and board technology )。

也许听到的最令人满意的公告是 1994 年 SEMATECH 的一项声明,互连技术从细间距外围互连到倒装芯片表面的面阵互连的“范式转变”是满足巨大的 1/ 0 不断发展的半导体业务的需求。 这一公告恰逢先进 ASIC、微处理器和电信设备对高频互连的需求。 对于世界大部分地区来说,这是一个范式转变,但对于 IBM 来说却并非如此,因为 IBM 在利基应用中使用倒装芯片(flip chips)已经有 35 年了。

我们很高兴在本书中分享我们对这项技术的经验和理解。

Karl Puttlitz 和 Paul Totta 都是 IBM SLT 开发的参与者,并且从一开始就见证并参与了芯片和封装设计技术的演进。 因此,他们是记录和编辑本面阵技术手册的合格人员。 同样令人高兴的是,他们邀请了来自世界各地的广泛参与者为这本书做出贡献,描述不同的经历。

我们希望这份参考书能够帮助新生和新工程师了解面阵技术、它是如何产生的以及如何应用它。 它还应该帮助需要深入了解该技术的经验丰富的实践专业人士,并将其应用或扩展到微电子封装的动态新世界。

“Fan-Out Wafer-Level Packaging(扇出晶圆级封装)”技术方向学术界的研究情况

图5. 近年来“扇出晶圆级封装(Fan-Out Wafer-Level Packaging)”的研究日益增多;

“Fan-Out Wafer-Level Packaging(扇出晶圆级封装)”技术方向研究较活跃的学术机构

“Fan-Out Wafer-Level Packaging(扇出晶圆级封装)”技术方向研究较活跃的学术机构:

- 科学技术研究局

- ASM国际

- 弗劳恩霍夫协会

- 柏林工业大学

- 中国科学院

- 安靠科技

- 鲁汶天主教大学

- 法国替代能源和原子能委员会

- 工业技术研究院

- 台积电

- 加州大学洛杉矶分校

- 东北大学

- 铟泰公司

- 星科金朋有限公司

- 三星

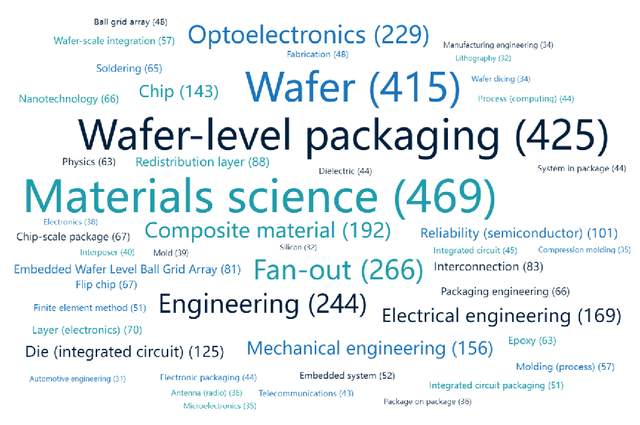

图6. 与“扇出晶圆级封装(Fan-Out Wafer-Level Packaging)”研究相关的关键技术词;

与“扇出晶圆级封装(Fan-Out Wafer-Level Packaging)”研究相关的关键技术词:

- Materials science

- Wafer-level packaging

- Wafer

- Fan-out

- Optoelectronics

- Computer science

- Composite material

- Electronic engineering

- Electrical engineering

- Mechanical engineering

- Chip

- Die (integrated circuit)

- Reliability (semiconductor)

- Redistribution layer

- Interconnection

- Embedded Wafer Level Ball Grid Array

- Layer (electronics)

- Chip-scale package

- Flip chip

- Nanotechnology

- Packaging engineering

- Soldering

- Epoxy

- Physics

- Molding (process)

- Wafer-scale integration

- Embedded system

- Finite element method

- Integrated circuit packaging

- Ball grid array

- Fabrication

- Integrated circuit

- Dielectric

- Electronic packaging

- Process (computing)

- System in package

- Telecommunications

- Interposer

- Mold

- Electronics

- Antenna (radio)

- Package on package

- Compression molding

- Microelectronics

- Manufacturing engineering

- Wafer dicing

- Lithography

- Silicon

- Automotive engineering

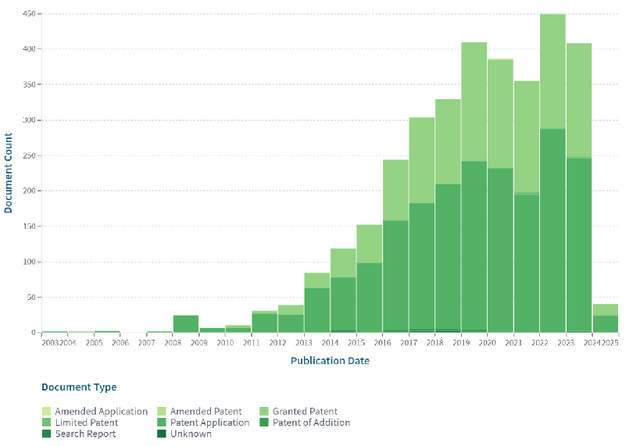

与“Fan-Out Wafer-Level Packaging(扇出晶圆级封装)”技术方向相关的专利申请情况

图7. 近年来“扇出晶圆级封装(Fan-Out Wafer-Level Packaging)”的专利申请日益增多

TSMC在“Fan-Out Wafer-Level Packaging(扇出晶圆级封装)”技术方向的专利申请较多

“Fan-Out Wafer-Level Packaging(扇出晶圆级封装)”技术方向专利申请较多的公司机构:

- Taiwan Semiconductor Mfg Co LTD

- Samsung Electronics Co LTD

- Stats Chippac Pte LTD

- Invensas Corp

- Qualcomm INC

- Applied Materials INC

- Sj Semiconductor Jiangyin Corp

- Infineon Technologies Ag

- Mediatek INC

- Samsung Electro Mech

- Freescale Semiconductor INC

- Deca Technologies INC

- Stats Chippac LTD

- Intel Corp

- Nxp Usa INC

图8. 与“扇出晶圆级封装(Fan-Out Wafer-Level Packaging)”相关的专利申请分类;

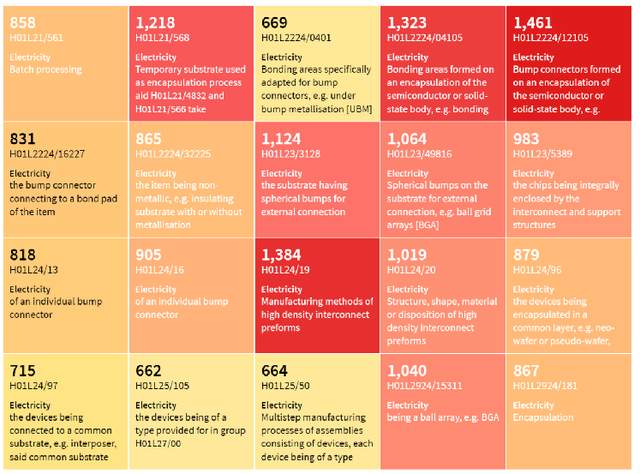

与“扇出晶圆级封装(Fan-Out Wafer-Level Packaging)”相关的专利申请文件