《完全集成 CMOS 无线接收器的 LNA-ESD 协同设计(LNA-ESD Co-Design for Fully Integrated CMOS Wireless Receivers)》一书介绍

日期:2021-09-21

这些都是美好的、令人安慰的哲学思想,应该永远记住。事实上,工程师们自己也遭受着对经济的强大控制。工程师为公司工作,公司有股东,股东需要利润来提高他们的个人生活质量,而不是提高社区的生活质量。然而,公司只能从有市场的产品中获利。市场的存在意味着全球社会的很大一部分受益于该产品。因此,不管经济状况如何,工程师们的目标都是服务于社区、设施和进步。

1.1无线通信市场的增长

最近取得进展的最突出的领域之一是电信世界。特别是无线通信领域,在过去的15年里取得了显著的增长。尽管无线通信这个术语非常现代,但它根本不是一个新概念。简单地和你旁边的人交谈,即使只是看一眼,也是一种明确无误的无线通信形式。第一种形式使用声波,并且对于现在的应用,带宽相当低。第二种通信实际上是无线光通信的一种形式。无线通信市场的指数级增长是一个普遍的现象。其中一个蓬勃发展的应用被称为全球定位系统或GPS系统。GPS旨在让用户计算出他相对于地球的位置。该系统由一组绕地球运行的卫星星座组成。这些卫星距离地球大约2万公里,每天完成2条轨道。共有24颗GPS卫星构成星座,它们在地球任何地方提供24小时GPS覆盖。

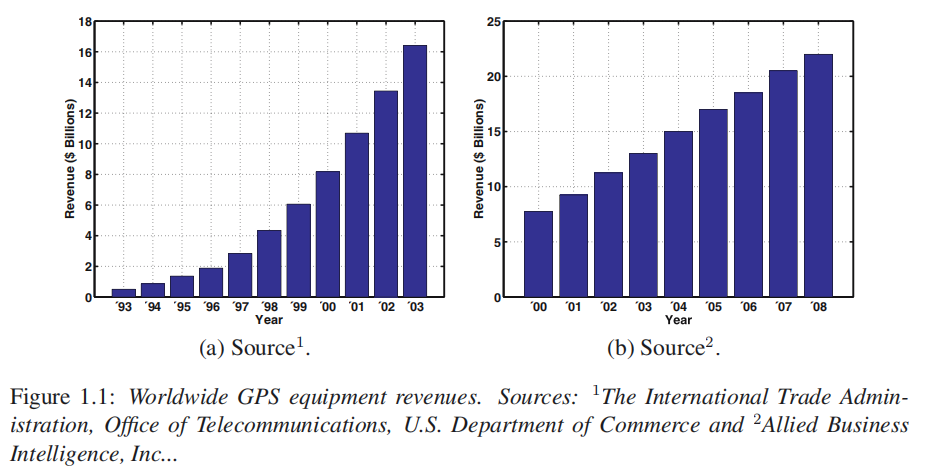

全球GPS收入如图1(a)所示。初始指数增长是明显区别的。1993年不到10亿美元,2003年每年超过160亿美元,平均年增长率超过25%。到2008年以后,全球GPS器件销售的收入将出现线性增长。一个中度的预测如图1(b)所示。

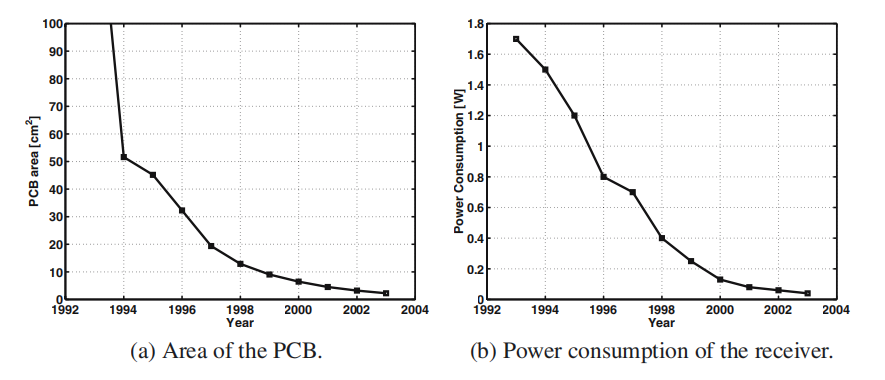

图2中所示,说明了GPS“引擎”到GPS接收器手表的演变。在图2(a)中绘制了典型GPS接收机PCB的面积。1993年,该面积通常在200到300平方厘米之间2。把这个笨重的GPS接收器放在你的手腕上可以比使用墙钟作为手表;相当不实用。而且在1993年,一个典型的GPS单元的功耗约为2W,如图2(b)所示。这将需要现代笔记本电脑的电池来给用户提供一到两天操作所需要的电量。这就解释了为什么单个GPS单元的价格很高,而且市场也非常有限。幸运的是,技术的进步每年将PCB面积减少了约50%,即大约每隔一年面积减少一半。今天的PCB的面积只有几平方厘米2 让它小到可以放进手表里。功耗的减少或多或少是相同的速度:从1993年的2W下降到今天的不到50mW。为了说明其后果,今天的CASIO手表允许根据位置更新频率接收GPS无线电使用一天或一天以上。随着GPS芯片面积和用电量的逐渐缩小,相应的价格也有所下降如图2(c)所示。同样,还可以区分同样的指数下降。此外,价格大约每隔一年降低成原来的一半。今天,一个GPS接收器的成本大约是几十美元(注:这是2003年的数据),而1993年的平均成本接近400美元。由于集成水平的不断提高,这种完整的进化是可能的。而集成是CMOS的核心能力。

1.2CMOSRF

CMOS自从在60年代早期最初发明以来已经走了很长的路。在十年后的70年代中期,人们推出了第一批工业产品。如今,CMOS是巨大、无处不在的数字IC市场的标准半导体技术。这就是为什么CMOS与罕见的Si双极性工艺技术,甚至更罕见的SOI技术、砷化镓或者SiGe技术相比价格相对较低,因此CMOS IC也用于模拟应用中。使用CMOS的另一个优点是,它提供了将射频和模拟基带电路与同一芯片上的数字处理器集成的能力。这有几个优点,例如:这种系统的面积减少了,因为它主要是在单个芯片上实现的。通过避免芯片外通常需要的耗功耗缓冲区,可以减少功耗。不幸的是,这里也有一些严重的缺点。数字处理的本质本身就会产生开关噪声。将敏感的射频放大器与数字处理器集成,两者之间共享基板导致基板中出现严重的开关噪声注入。这种开关噪声的存在可能会严重扰乱前端的灵敏度。这就是这些完全集成的系统仍然很罕见的原因之一。尽管可以采取几种预防措施来减少这种噪声耦合,但它们还不足以用于高性能的应用。商业单片机CMOS收发器最近已经可用于一些低端应中,如蓝牙芯片。另一个缺点是去除射频前端的外部组件。这通常会迫使用户迁移到不同的电路拓扑结构。例如,在经典的超外差接收机中,下变频转换是通过几个步骤来完成的。这需要中间高Q滤波来进行所有阶数后的镜像干扰分量的消除。这种拓扑结构对于一个完整的CMOS无线接收器并不有趣,因为这些高质量的混合器必须在外部实现,而且它们会过度增加整个系统的成本。因此,业界还设计了另外两种不需要这些高滤波器的拓扑结构:零IF接收器和低IF接收器。两者都是直接转换接收器,因为它们不需要第二个下变频转换步骤。

尽管在提供一个完整的集成收发器方面存在这些持续的障碍,但由于CMOS固有的低成本,它仍在成为射频应用的一个有吸引力的候选器件设计方案。

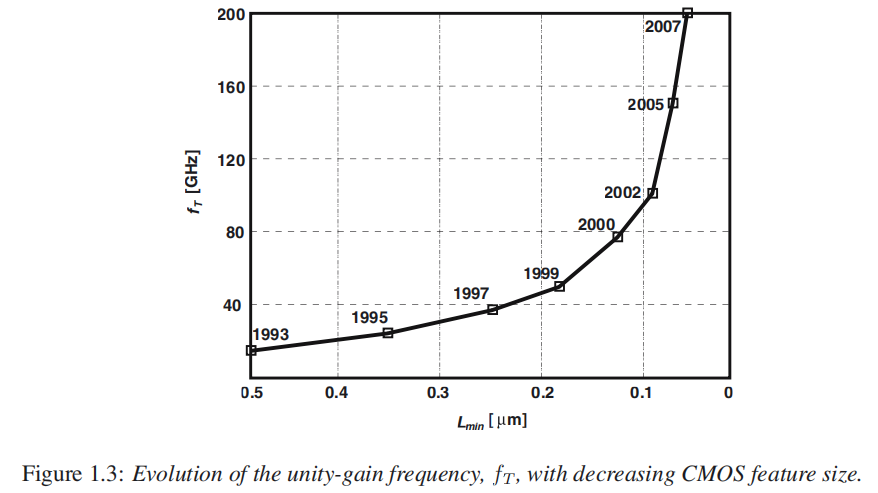

此外,随着工艺技术的缩小,提高数字集成电路的速度和降低功耗,fT(单位电流增益频率)也会增加,这本质上允许更高的频率操作。fT与CMOS工艺技术的特征尺寸大小如图3所示。同时,图中还指出了该技术已经或将投入使用的年份。一般认为,CMOS射频接收器对于应用在大约低于fT/10的频率是可行的.一个很好的例子是有研究者提出的2VCMOS单位收发器前端。它已经在早期的0.25µ技术中实现,对应于一个fT最大值约30GHz。该收发器完全集成,工作在1.9GHz,或多或少证实了上述经验法则。目前新兴的标准90nm CMOS技术提供了一个fT接近100GHz。这意味着这些技术将允许完全集成的射频接收器高达10GHz。对于5-6GHz无线局域网标准IEEE802.11a和无线用户来说,这就足够了。当然,这一经验法则应该谨慎使用,因为这在很大程度上取决于系统规格要求。对于发射器部分,除功率放大器外,经验法则或多或少是相等的。在那里,较小工艺节点的技术的较低的击穿电压抵消了fT和fAx的增加. 根据所需的输出功率,可能需要使用更专用的技术中在外部实现功率放大器。

1.3CMOS、RF和ESD

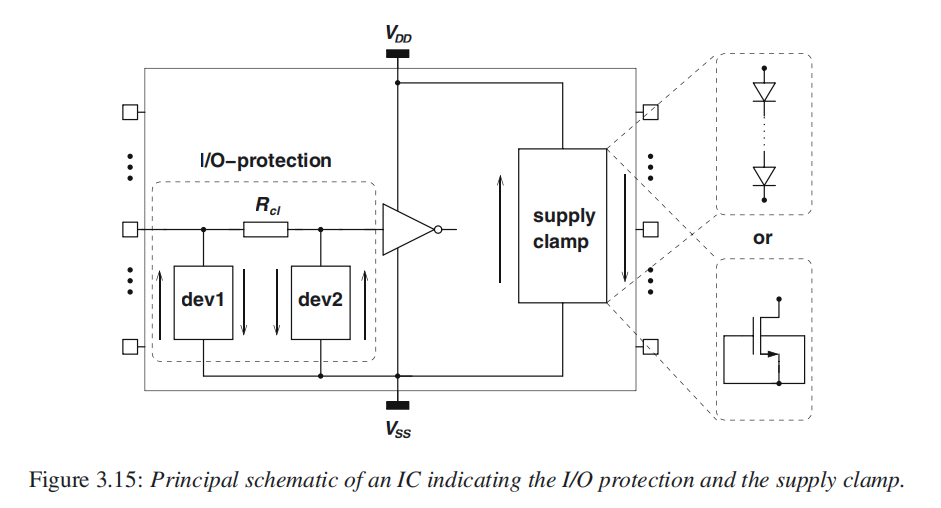

对于任何在经济上可行的产品,可靠性都是一个严重的问题。这也适用于集成电路的世界。在这种情况下,可靠性是指的是几个不同的主题。当一个产品在所有正常情况下应该做的事情时,它是可靠的。对于集成电路,这意味着电路需要在规格和所有可能的条件下运行,包括温度、湿度等。自然,在两个IC之间存在一个固有的偏移量,这是由于工艺参数不可避免的波动造成的。直通率是指芯片在规范范围内工作的百分比。一个大的直通率对于一个成熟可靠的产品来说是必不可少的。另一个可靠性领域要求电路在正常和异常的人或机器处理下保持功能。这将使我们立即了解到该电路对静电放电或ESD的抵抗力。任何上市的集成电路都被认为对ESD有一定的内置免疫力。所需的保护量取决于应用的需要。直接连接到外部世界的IC PIN脚比仅在产品内部使用的增加更容易受到ESD事件的影响。对于射频接收机,输入可以立即连接到外部天线。这直接将IC暴露于通过导电天线的人静电放电中。虽然这是一个极端的例子,但每个芯片在移动、包装和组装过程中都会与机器和或人类接触。在任何这些行动中,他们都可能暴露于ESD的危险中。这就是为什么将集成电路组装成中间产品或最终产品的公司通常需要他们有ESD保护。

事实上,将CMOS射频电路引入市场的最后瓶颈之一是它们对ESD的敏感性。这是由于栅极氧化物击穿和半导体结恶化相关的问题。在缩小的技术中,氧化物厚度的减少和掺杂水平的增加进一步加剧了它们。大多数CMOS esd保护电路结构(例如,因为它们被用于数字CMOS)的寄生参数可能会对射频性能有害。

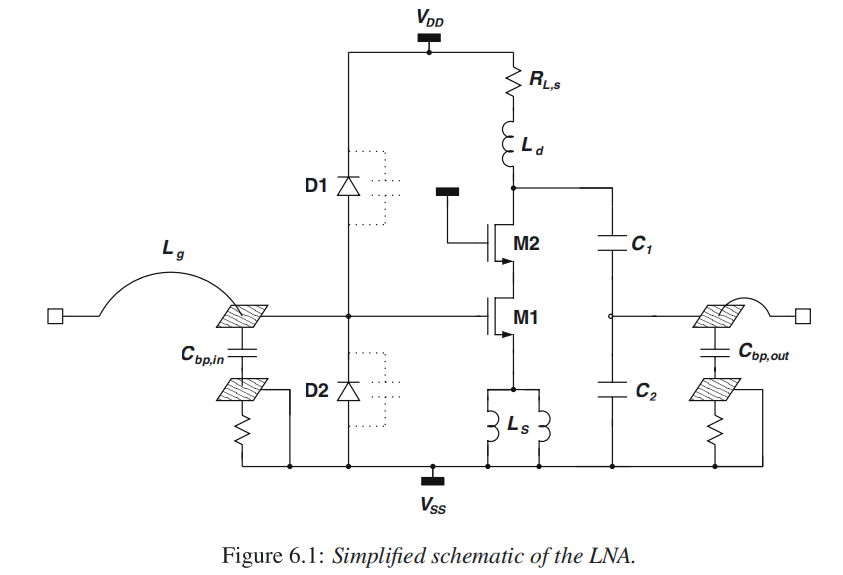

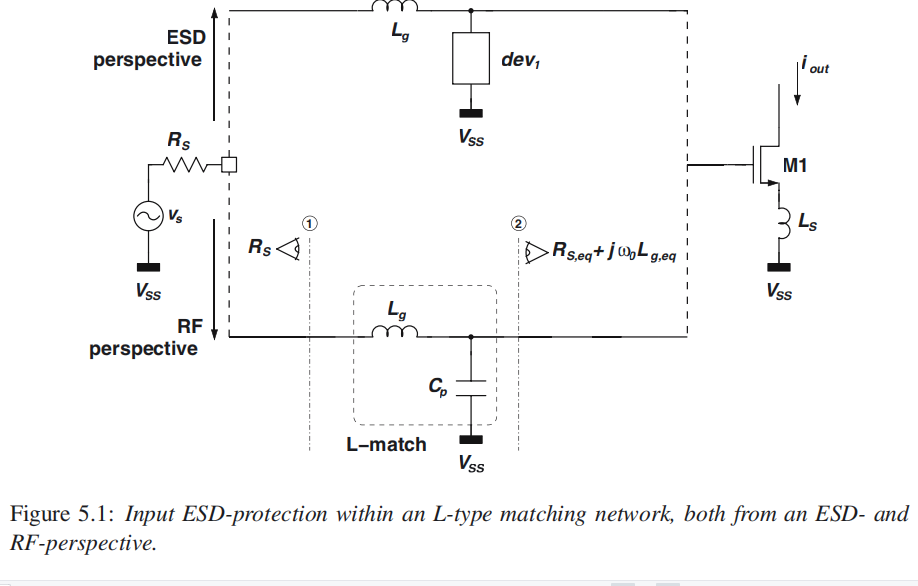

受ESD要求影响最大的电路模块之一是低噪声放大器。因为它是任何集成接收机中的第一个功能模块。LNA的目标是在不增加大量噪声的情况下,尽可能多地放大射频输入信号。应用规定了相应的最低信号水平应提升至后续混合器阶段的底噪以上。LNA的低噪声性能使它非常容易受到任何输入寄生信号的影响。当然是电阻,也可能是电容和电感寄生可能严重恶化噪声性能。esd保护电路具有电阻性和电容性寄生效应,不可避免地降低LNA的噪声系数。本文将深入研究防静电约束条件对射频低噪声放大器设计的影响。现代GPS接收机的灵敏度要求使GPS LNA成为设计esd保护LNA的理想演示器。我们将研究经典的防静电保护电路和器件如何影响射频性能。本书将提出新的拓扑结构来克服经典ESD电路的性能限制。这些拓扑结构需要进行严格的LNA和ESD保护的协同设计。

1.4这本书的大纲

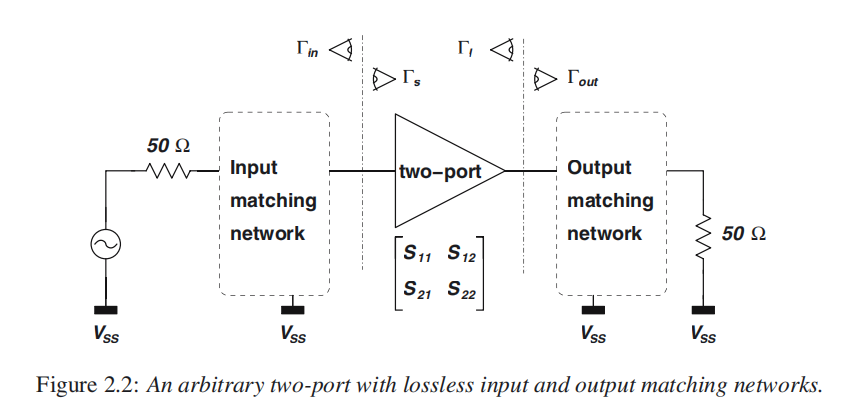

•第二章简要概述了CMOS无线接收机的低噪声放大领域。它首先简要介绍了最重要的射频概念。本文解释了将用于手工计算的器件模型。这些手工计算将应用于整个文本来解释电路的行为。这些模型足够简单,可以使所得到的方程易于管理。它们又足够复杂,可以准确地描述这些重要的现象。模型的参数可以适用于仿真结果,以提高局部或全局的精度。这些模型和计算将重复用于生成不同设计和性能参数的等高线图。这些图旨在让直观地了解电路的行为。本书介绍了一种与数值模拟器一起使用的扩展MOS模型。在一般介绍了噪声之后,在接收机链路内描述了LNA功能。得出了主要的设计标准和性能要求。本章最后,对CMOS中最常见的LNA拓扑进行了分类和讨论。一些特定和有趣的设计以及发表在开放文献中,但超出上述分类也书中被澄清了。

•第三章快速调查不同的静电测试和标准以及各种静电保护装置和拓扑。人体模型测试最常用的标准之一是基于人体模型测试(HBM)。保护量由电路能够承受的HBM电压表示。IC的标准保护等级为2kV。

•第4章将详细讨论射频LNA最有趣的拓扑结构之一,即具有感应源极退化的共源极LNA。它之所以如此有趣,是因为它能够实现极低的NF和高增益,这对于当今许多需要良好灵敏度的无线接收器(GPS、GPS、GSM、DCS1800、UMTS等)来说是必需的。所有相关的寄生成分所产生的影响都将在本章中被讨论到了。它们对不同性能标准(噪声、增益、线性、匹配和稳定性)的影响将通过相关的设计方程来解释。数值评估是基于在1.5GHz LNA中使用0.25µ CMOS工艺技术的设计进行演示说明的。

•第5章专门介绍了新的射频-ESD协同设计方法,能够满足高频LNA的射频和ESD要求。讨论是基于具有源极退化电感器的CS(共源极)LNA,但最后扩展到其他拓扑。本章首先回顾了经典CS LNA的频率限制。介绍了两种不同的RF-ESD协同设计策略来克服这些限制。第一种技术是基于使用Π型输入匹配网络。第二种解决方案使用一个芯片上的电感器来排出(drain)掉ESD电荷。在相同的0.25µ工艺技术下,采用5GHz演示设计对不同方法进行数值评估。

•第6章讨论了三种LNA原型机的设计、布局和测量方法。所有电路都配备有esd保护装置。第一个芯片是用于1.23GHz的L2频段的GPS低噪声放大器。它已采用0.25µ工艺技术实现。第二个低噪声放大器已被设计并集成在一个完整的L1频段的GPS接收器前端。它已经采用了同样的技术来实现。最后的设计针对5个GHz无线局域网应用程序。该电路具有一个集成的esd保护电感器。